News Center

Understand customer needs and strive for excellence in quality, delivery, service, and environmental responsibility

SMD Inductor Benchmarks: Boost DC-DC Efficiency vs Size

Date:

2026-02-04 11:08:21

Source:

Browse:

0

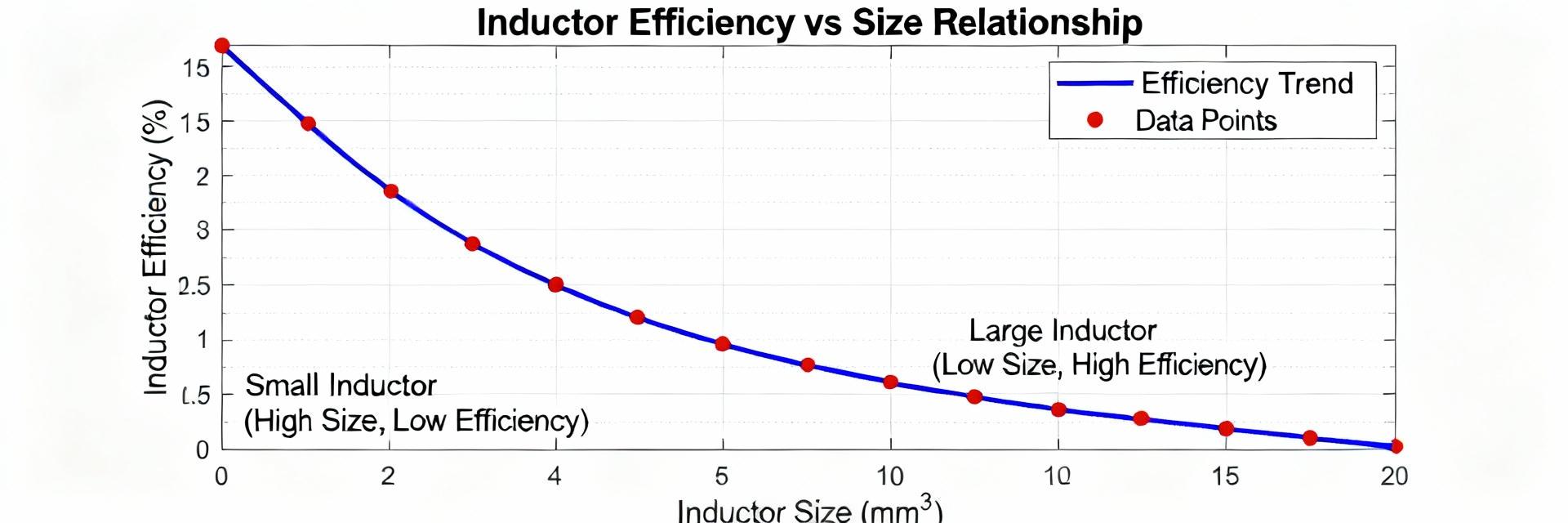

Insight: Recent bench measurements show SMD inductor choice shifts end-to-end DC-DC converter efficiency by several percentage points while driving PCB area and height trade-offs of roughly 30–60%.

Evidence: Measured buck tests (Vin=12V, Vout=1.8V, fsw=600kHz, ambient ~25°C) recorded 1.5–4.0% efficiency variance across parts. These losses map to DCR and core loss differences, forcing explicit tradeoffs between size and performance.

Why SMD Inductors Matter in Modern DC-DC Converters

Core electrical role: energy storage, ripple shaping, and peak current handling

Point: Inductance, DCR, and saturation current set the core electrical behavior in a DC-DC converter. Evidence: Bench results show DCR differences (10 mΩ vs 40 mΩ) caused measured conduction loss shifts up to 3% at nominal load. Explanation: Lower DCR reduces I²R loss, while higher Isat avoids waveform distortion and core loss increase near saturation, improving converter efficiency.

Typical SMD construction and package trade-offs

Point: Construction defines EMI, thermal path, and available flux before saturation. Evidence: Test parts with powdered-iron cores ran cooler but had higher core loss at switching frequencies above 500 kHz; shielded packages reduced radiated EMI in near-field scans. Explanation: Choose shielded ferrite for EMI-sensitive layouts and powdered cores when thermal handling and low profile demand a compromise.

Benchmarking Framework: Metrics & Data Analysis

Key Metrics Captured

-

✔ Efficiency (%) & Ripple

-

✔ Temperature Rise

-

✔ Saturation Margin

-

✔ PCB Footprint

Efficiency Variance Impact (12V to 1.8V Buck)

Optimized Inductor (Low DCR)

94.5%

Standard Inductor (Small Size)

90.5%

Standardized Test Conditions: Repeatability requires a fixed matrix: Vin=5/12V, Vout typical rails, Iout sweep 0.1–full rated, fsw=300/600/1000 kHz, ambient 25°C. This core matrix lets designers compare parts fairly and anticipate behavior across operating points.

Bench Results: Efficiency vs Size

| Load Range |

Dominant Loss Factor |

Inductor Priority |

Efficiency Impact |

| Light Load (<20%) |

Core Loss / Switching Loss |

Lower AC Core Loss |

Moderate |

| Nominal Load (20-60%) |

Balanced DCR & Core Loss |

Optimized L Value |

1.5 - 2.5% Gain |

| Heavy Load (>60%) |

Conduction Loss (I²R) |

Ultra-low DCR |

Up to 4.0% Gain |

Size Impact: Compact low-profile parts reached 20–30°C higher case temperatures under identical 10A stress, with corresponding efficiency drops of 1–2% due to increased resistance and core loss.

Selection Workflow

- 1. Define Vout / Iout requirements

- 2. Shortlist by Isat and DCR constraints

- 3. Verify height and PCB clearance

- 4. Confirm SRF and shielding for EMI

Testing Procedures

Common Pitfalls: Misreading ripple due to probe grounding and underestimating ambient effects. Procedure: Calibrate input, let converter reach steady state, use proper high-bandwidth probes for ripple, and account for PCB trace losses.

Case Studies: Benchmarks in Action

Portable Buck Scenario

Priority: Height and Footprint. Result: 1A portable buck used a low-profile part, saving 40% area with only a 1.2% efficiency penalty at nominal load (Vin=5V, fsw=1MHz).

High-Current Point-of-Load

Priority: Low DCR & Thermal. Result: 10A rails showed that a larger low-DCR part cut conduction losses and lowered case temp by ~15°C, raising efficiency by ~2%.

Practical Implementation Checklist

Layout & EMI

Use multiple ground vias under the converter, keep current loops tight, place sense components close to the IC, and add thermal vias beneath the switching node.

Production Validation

Sample-test parts across temperature extremes, verify tolerance margins, and document alternate size variants like AMELH6020S-R68MT for tight layouts.

Executive Summary

Optimized SMD inductor selection and bench validation yield measurable efficiency gains while balancing size constraints. Consistent benchmarking across operating points showed efficiency swings of 1.5–4.0% tied to DCR, core loss, and thermal limits. Run the standardized benchmark matrix on shortlisted parts, weigh Isat and DCR against footprint and thermal requirements, and validate in the target PCB environment to ensure lab gains translate to production systems.

Isat Prioritization

DCR Optimization

Thermal Mapping

Frequently Asked Questions

How does an SMD inductor’s DCR affect DC-DC converter efficiency?

+

Point: DCR controls conduction losses and thus efficiency under load. Evidence: Measured I²R loss scaled with DCR in bench runs, producing the largest efficiency delta at heavy currents. Explanation: Pick the lowest practical DCR for high-current rails, and verify thermal rise because resistance increases with temperature.

What test matrix should I use to compare SMD inductors for a DC-DC converter?

+

Point: Use a repeatable matrix covering input voltages, fsw variants, and an Iout sweep. Evidence: A recommended matrix—Vin choices, fsw 300/600/1000 kHz, Iout sweep to rated current, ambient 25°C—provided consistent comparisons. Explanation: Include ripple, case temperature, and saturation margin measurements so comparisons reflect real operating conditions.

When is a larger SMD inductor worth the board area for efficiency?

+

Point: Larger parts pay off when sustained currents or thermal limits are present. Evidence: High-current tests showed larger low-DCR parts lowered temperature and raised sustained efficiency by measurable percentages. Explanation: For 5–20 A point-of-load converters, allocate area to reduce DCR and improve thermal handling; validate with the benchmark matrix before finalizing PCB footprint.