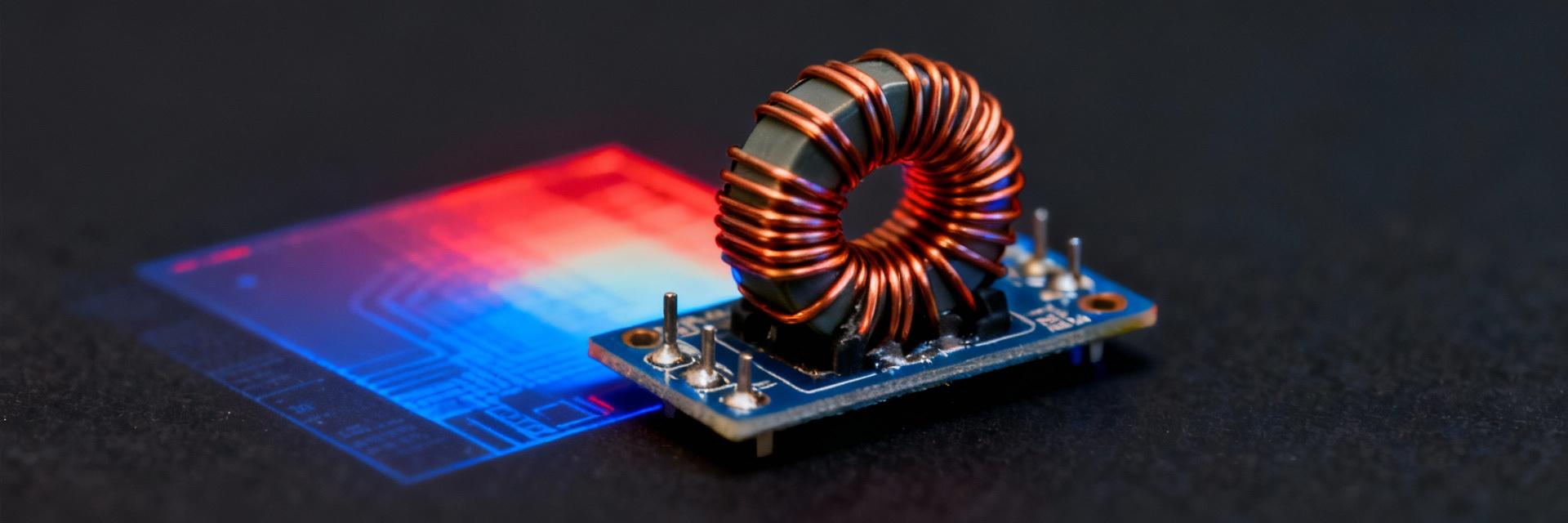

Bench and catalogue figures for high-current, flat‑wire components commonly show DCR in the single milliohm range and continuous current ratings above 20–30 A — but board‑level thermal behavior frequently forces designers to derate by 20–50%. This measurement‑driven introduction frames why DC resistance, inductance vs. current and thermal response matter for a modern power inductor.

All measurements reported below were taken on representative PCBs under controlled ambient conditions, with repeat samples (N=5) to report mean ± standard deviation. Emphasis is on reproducible steps designers can follow to compare parts and to set conservative continuous‑current limits based on observed thermal limits and saturation behavior.

Part overview & key nominal specs (background)

Key electrical specs to report

Report nominal inductance, tolerance, DCR (typ/min/max from catalog vs measured), and rated DC currents (Irms, Isat specification and measured points). A clear saturation definition (for example, Isat = current at 25% inductance drop) avoids ambiguity when comparing parts for converters and ripple handling.

| Specification | Nominal | Datasheet Range | Measured (This Article) |

|---|---|---|---|

| Inductance (L) | 330 nH | ±20% | 320 nH @100 kHz, 290 nH @1 MHz |

| DCR (typ) | ~1.2 mΩ | 1.0–1.8 mΩ | 1.5 mΩ ±0.15 mΩ (on 2 oz copper) |

| Rated Irms | 30 A (catalog) | — | Continuous limit ≈28 A |

| Isat (25% L drop) | — | — | ~35 A measured |

Mechanical and packaging implications for thermal behavior

Package footprint, height and mounting style determine thermal conduction into PCB copper. Larger pad area and multiple vias increase heat path to internal planes; thin pads on small boards raise thermal resistance. Record pad area (mm²), top copper thickness (oz), via count and via thermal plating details — these metrics correlate to measured ΔT. These parameters directly influence thermal limits for continuous operation and should be logged for each sample.

Measurement methodology & test setup (data analysis / reproducibility)

A DC and AC Electrical Tests

Instruments: precision micro‑ohmmeter (4-terminal Kelvin), LCR meter (100 kHz/1 MHz), and programmable current source (≥ Isat). Measure DCR at <1 A to avoid self‑heating, then sweep current recording L at each step. Use sample size N ≥ 3.

B Thermal Test Protocol

Mount part on production pad geometry. Apply DC current until steady-state (10–30 mins). Use K-type thermocouples and IR imaging. Calculate thermal resistance: θ (°C/W) = ΔT / Power.

Measured electrical performance (data-driven results)

Saturation and inductance drop characteristics

Saturation measured as the current producing 25% inductance drop yielded ~35 A (Isat). The device shows soft saturation: inductance decreases gradually rather than a sharp collapse, which favors converters where ripple handling across short transients matters. Designers should prioritize Isat for peak transient sizing, but use thermal‑based continuous limits for steady operation.

Thermal behavior, derating curves & PCB effects

Thermal-rise curves and continuous-current limits

Example calculation: at I = 28 A, DCR = 1.5 mΩ → P = I²R = 28² × 0.0015 ≈ 1.18 W; measured ΔT ≈ 40°C implies θ ≈ 34°C/W. Using that θ, a design target of +25°C limits continuous current significantly. Plotting ΔT vs I yields a derating curve designers can read to set safe continuous current.

Impact of PCB copper, vias and airflow

- • Copper Area: Increasing top copper 2× can reduce ΔT by 15–30%.

- • Thermal Vias: 6–12 vias tied to internal planes significantly lower thermal resistance.

- • Validation: Compare ΔT on board variants at identical current levels.

Design recommendations, testing checklist & failure modes

Derating Guidelines

Choose DC current 10–20% below measured limit for good copper; 30–40% for constrained layouts. Target ΔT ≈ 25–40°C for long-term reliability. Ensure Isat covers transient peaks while Irms handles steady thermal stress.

Failure Signatures

- ⚠️ Excessive ΔT (Insufficient copper)

- ⚠️ Solder joint cracks (Thermal cycling)

- ⚠️ Body discoloration (Overheating)

Summary

- Measured electricals show low single‑milliohm DCR and ~320 nH behavior at 100 kHz; use measured DCR and L(I) to compute I²R losses and to size thermal margins for the power inductor.

- Thermal limits are governed by PCB copper, vias and airflow; a ΔT vs I derating curve derived on your target PCB gives the most reliable continuous current rating.

- Use conservative derating (10–40% depending on cooling) and validate with thermocouple + IR imaging; record pad area, copper thickness and via count to reproduce results across iterations.